Development of an open gate dielectric process for SiC MOSFET manufacturing SOPO Task #BP2-2.17 CFP28 Auburn University

Presenter: Ayayi Claude Ahyi (AU)

Key Team Members: Sarit Dhar (AU)

Kevin Matocha (Monolith. Semi.)

Students Members: Yongju Zheng, Benjamin Schoeneck, Daniel Jeziorski

## Motivation and Objective

- Nitrogen passivation of the interface is the established technology. All methods

of inserting nitrogen plateau around the same mobility values

- In this project we are looking beyond Nitrogen using a series of short loop experiments. Lateral MOSFETs of 4 promising technologies are tested:

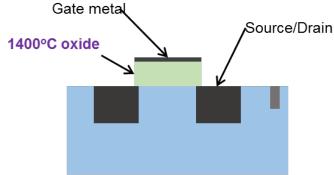

- Ultra-High temperature oxidation

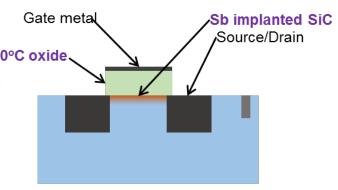

- Ultra-High temperature oxidation with Sb counter doping for higher Field effect mobility

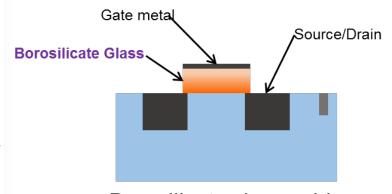

- Boro-Silicate Glass (BSG) oxide devices

- Ge strained SiC devices

- The most performant in terms of mobility, stability, oxide strength and compatibility with current fabrication process will be selected for a test run of DMOSFETs

## Ultra High Temperature Oxidation

Easier desorption of the Carbon from the interface

Ultra high temperature oxidation

Counter doped Ultra high temperature oxide

### **BSG MOS devices**

1176

IEEE ELECTRON DEVICE LETTERS, VOL. 35, NO. 12, DECEMBER 2014

# Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation

Dai Okamoto, *Member, IEEE*, Mitsuru Sometani, Shinsuke Harada, Ryoji Kosugi, Yoshiyuki Yonezawa, and Hiroshi Yano, *Member, IEEE*

Abstract—We propose another process for fabricating 4H-SiC metal-oxide-semiconductor field-effect transistors (MOSFETs) with high channel mobility. The B atoms were introduced into a SiO<sub>2</sub>/4H-SiC interface by thermal annealing with a BN planar diffusion source. The interface state density near the conduction band edge of 4H-SiC was effectively reduced by the B diffusion and the fabricated 4H-SiC MOSFETs showed a peak field-effect mobility of 102 cm<sup>2</sup>/Vs. The obtained high channel mobility cannot be explained by counter doping because B atoms act as acceptors in 4H-SiC. We suggest that the interfacial structural change of SiO<sub>2</sub> may be responsible for the reduced trap density and enhanced channel mobility.

Index Terms—Boron passivation, channel mobility, interface state density, SiC MOSFETs.

I. Introduction

Several researchers have suggested that the near-interface traps (NITs) located near the  $SiO_2/4H$ -SiC interface may be related to the  $D_{it}$  near the conduction band edge of 4H-SiC [4], [10]. Although there have yet to be detailed theoretical and experimental studies on NITs, the removal of interface stress may be effective in reducing NIT density [4], [10]. To reduce interface stress, it may be effective to incorporate network formers such as  $P_2O_5$  into the interface because they reduce the connectivity of the  $SiO_2$  network and thus reduce interface stress [13]. Based on the above considerations, we hypothesize that the incorporation of B may also be effective in reducing the interface stress and thus in reducing the trap density because  $B_2O_3$  is also known to be a network former that reduces the network connectivity of  $SiO_2$  [14].

In this letter, we describe that the channel mobility of

Borosilicate glass oxide

#### Ge:SiC

APPLIED PHYSICS LETTERS VOLUME 74, NUMBER 4

25 JANUARY 1

#### Electrical and optical properties of Ge-implanted 4H-SiC

G. Katulka<sup>a)</sup>

U.S. Army Research Laboratory, Weapons and Materials Research Directorate, Aberdeen Proving Ground, Maryland 21005-5066

C. Guedj and J. Kolodzey

Department of Electrical and Computer Engineering, University of Delaware, 140 Eyans Hal.

APPLIED PHYSICS LETTERS

VOLUME 85, NUMBER 12

20 5

#### Pseudomorphic SiC alloys formed by Ge ion implantation

M. W. Dashiell, <sup>a)</sup> G. Xuan, E. Ansorge, X. Zhang, and J. Kolodzey<sup>b)</sup>

Department of Electrical and Computer Engineering, University of Delaware, Newark, Delaware 19716

G. C. DeSalvo, J. R. Gigante, W. J. Malkowski, and R. C. Clarke

Northrop Grumman, Advanced Materials and Semiconductor Device Technology Center; Baltimore,

### Influence of 250 keV Ge ions fluence on electrical and optical properties of SiC

M.S. Rafique<sup>a</sup>, N. Tahir<sup>a,b,\*</sup>

<sup>a</sup>Physics Department, University of Engineering and Technology, Lahore, Pakistan <sup>b</sup>National Centre for Physics, Islamabad, Pakistan

Received 25 July 2006; received in revised form 10 January 2007; accepted 10 January 2007

#### Abstract

Commercially graded SiC samples were implanted with 250 keV germanium ions (Ge<sup>+</sup>) at room temperature. For Ge<sup>+</sup> ions so laser-induced plasma (LIP) technique was used. Ge<sup>+</sup> implantation was confirmed by energy dispersive X-ray (EDX) analysis. Chan FWHM and lattice constant of SiC samples has been observed after the Ge implantation, calculated by Bragg's law from XRD and A comparison of the electrical and optical properties of SiC before and after Ge<sup>+</sup> implantation (SiC:Ge) has also been made. Elec diagnostic comprises of a four-probe method for the measurement of resistivity whereas Raman spectroscopy is employed for the op investigation. Resistivity measurements of SiC and SiC:Ge samples showed that resistivity decreases as Ge<sup>+</sup> implantation increase and the siC:Ge showed that Raman band became broadened and is shifted towards the lower wave nu with the increase in Ge ion fluence. The increase in Ge ions fluence enhances the lattice defects which are responsible for broadeni XRD and Raman peaks as well as increase in conductivity of the samples.

© 2007 Elsevier Ltd. All rights reserved.

Ge Strained SiC channel

- Evidence of strain in the SiC lattice

- Lower resisivity

# What has been accomplished so far

- Fabrication of the of the common template for the devices up to Gate oxide or Gate implant steps.

- Ultra High Temperature Oxide MOS capacitors and MOSFETs

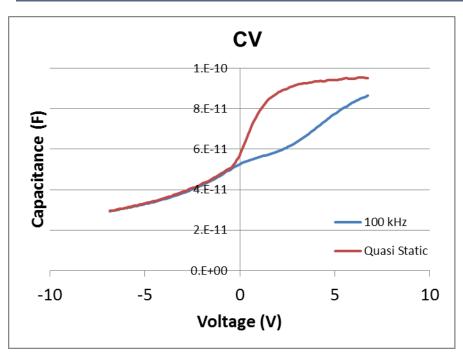

- Borosilicate Glass Devices :

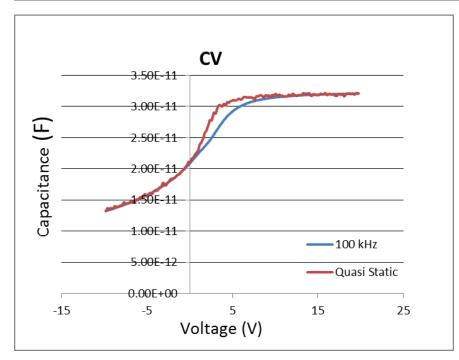

- Evaluation Borosilicate glass obtained by different methods using MOS capacitors

- Characterization of BSG MOSFETs from B<sub>2</sub>O<sub>3</sub> solid Source

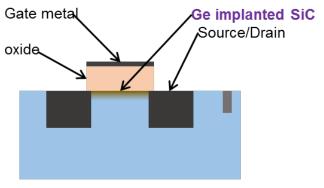

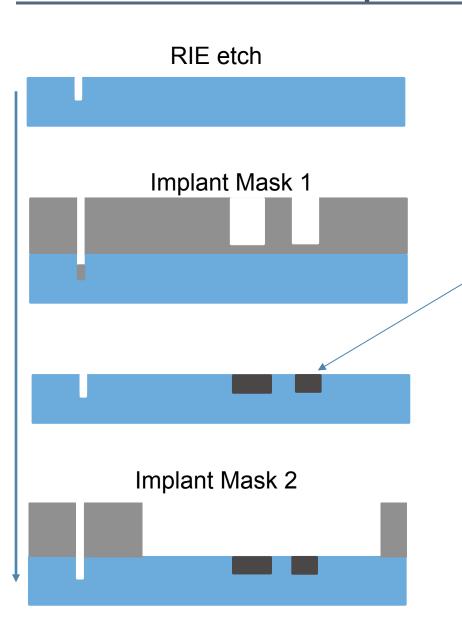

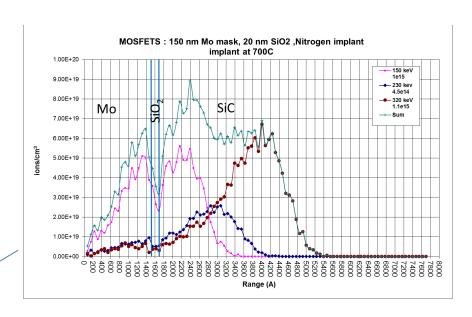

# Common Template for all devices

Source/Drain implant

# Doping profiles

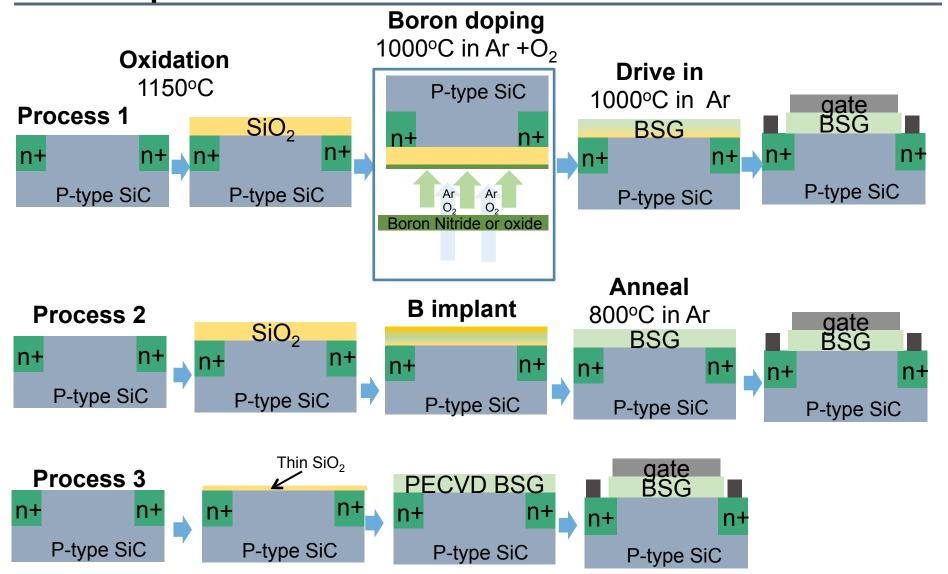

### BSG processes

# BSG gate oxide devices

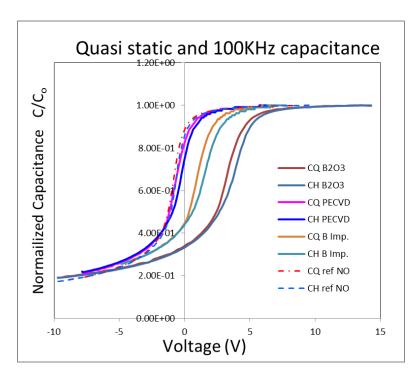

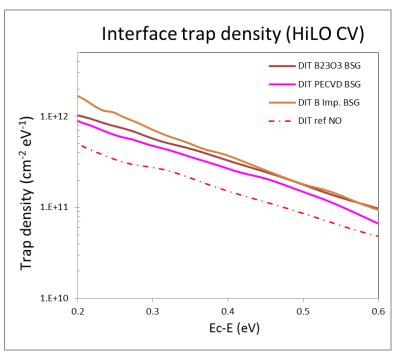

#### BSG gate oxide devices: comparison of B doping methods

BN solid source doped devices showed too weak oxides to be fully characterized. They have been dropped from the study. The high interface trap density of the implanted Boron devices also shows more in depth work would need to be done on these device. Therefore they were also dropped from this study.

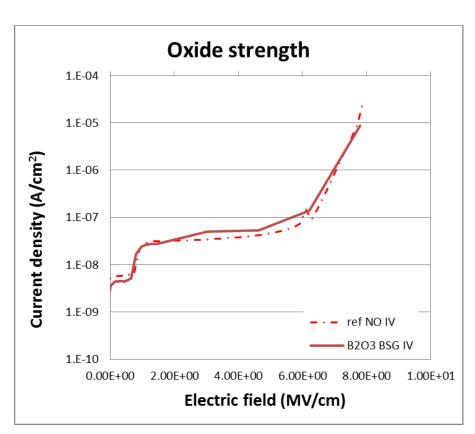

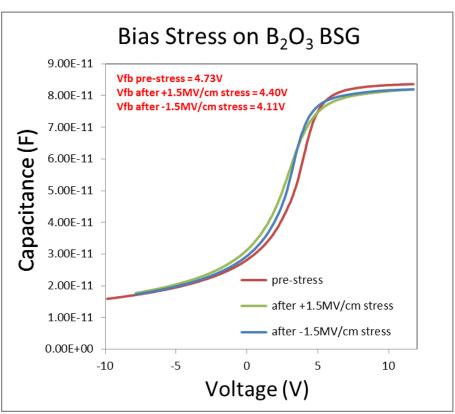

# BSG: Oxide strength and stability

BSG gate oxide devices: stability and reliability

Preliminary results have been obtained in oxide breakdown strength and reliability

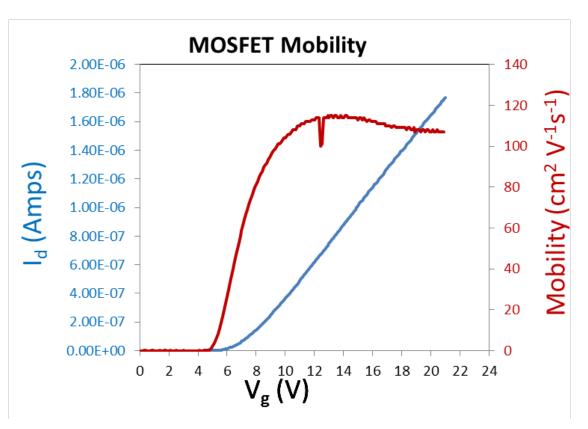

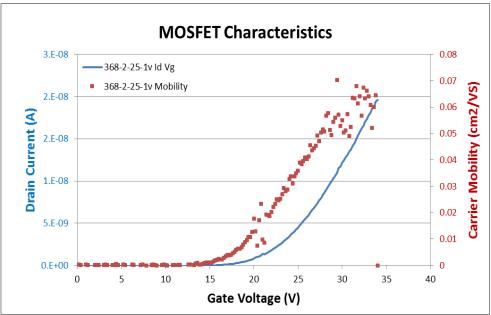

# BSG MOSFET (B<sub>2</sub>O<sub>3</sub> source)

- Devices show high field effect mobility

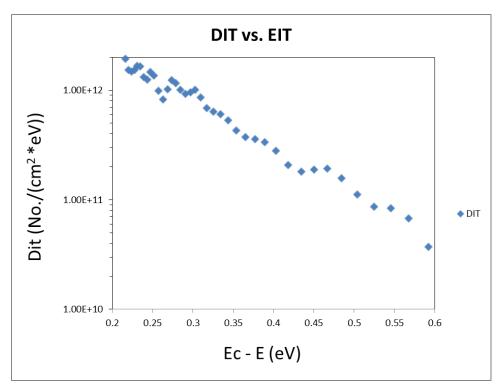

- Reduced interface trap density

- Residual instability is possibly due to impurity in the doping material

- Deposited BSG shows great promise in reducing unwanted impurities

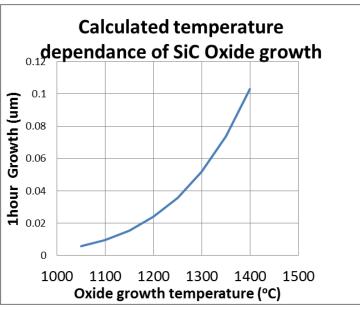

## Ultrahigh temperature Oxidation

- Process 1

- Oxide growth at 1425°C

- Ramp up and ramp down under Ar flow

- Process 2

- Oxide growth at 1150°C

- Anneal in Ar at 1500°C

### 1425°C oxidation

- Low Mobility

- Significant Gate leakage

- High contact resistance due to Al contact

- 10 min in O<sub>2</sub> at 1425°C

- Ramp up and down in Ar

- Thicker than expected oxide, suggests oxidation during rampu up and ramp down

- High trap density; The interface seems unpassivated

### 1500°C Ar Anneal

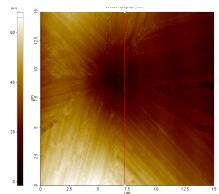

AFM Image of the oxide shows dendrite-like defects, possibly due to crystallization

- Interface trap density similar to unpassivated oxides

- Original process requires extremely fast cooling that could not be replicated. Ramp down was limited to 5º/min to avoid cracking the furnace tube

### Conclusion

- So far Ultra high temperature oxidation did not show any advantage in trap density reduction, oxide strength or carrier mobility.

- A fair evaluation of ultra high temperature oxidation requires process equipment with higher performance to reduce parasitic growth, contamination and cooling rate.

- Devices with Ni ohmic contacts will be made.

## Remaining Work

- Sb counter doped Ultra High temperature oxide devices.

- Revisit Ultra High temperature oxide devices with improved set up

- · Ge strained SiC devices